# Au5508: Quad PLL Frequency Translator / Jitter Attenuator / Network and Port Synchronizer / AAU Clock

## **General Description**

Au5508 offers most integrated 5G clock solution: Combines BBU, Wireline, AAU, Serdes requirements in one part definition.

- Unique integration of Sync Features

- Enables Systems with Low Constant Time Interval Error

- IEEE1588/SyncE/1 PPS full support

- Lower jitter for higher data rate links

- Lower close in noise and JESD204B/C full support for AAU RF clocks

- Integrated feature rich single part offers unparalleled flexibility to the system designer

#### **Features**

- Ultra Performance PLLs

- Fully Integrated design with no external components

- 120 fs Typical RMS integrated jitter (12k-20M)

- 122.88M Output with excellent close in noise performance

- Fully Flexible Output and Input Mux: High level of flexibility in output allocation for PLLs

- JESD204B/C Support for data converter clocks

- 1 PPS Input / Output Support with sub 20s lock time

- External EEPROM Support

- TDC Mode available on all input clocks to measure input delays with < 10 ps accuracy: 10 TDC Channels available (independent of the PLLs)

- Frequency Control DCO: DCO Control on all outputs (down to 1/16 ppt)

- Phase Control DCO: Fine phase adjustment knob for phase of all outputs from a PLL (adjustment accuracy < 1ps) in both closed loop and open loop modes</li>

- Internal modes to combine wander of OCXO with jitter of XO for holdover— Provides 24 hour holdover with programmable HO accuracy settings

- Best in class hitless switching performance: PBO with sub 25 ps hit, Phase Propagation & Frequency Ramp with programmable freq/phase slopes

- Fully integrated Jitter and wander attenuation options down to 0.09 mHz

- Repeatable input to output delays with output relative delay adjust

- Internal ZDB Mode with < 0.5 ns Input to Output delay independently available for each PLL

- Outputs can be phase aligned an independent sync pulse

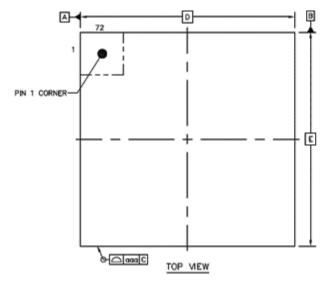

- 72 QFN 10mm X 10mm Package

| Product Family | Inputs / Outputs                                          | Input Freq       | Output Frequency       | RMS Jitter   | Packages |

|----------------|-----------------------------------------------------------|------------------|------------------------|--------------|----------|

| 55xx           | 5 Diff / 10 SE Inputs<br>Up to 12 Diff / 24 SE<br>Outputs | 0.5 Hz - 2.1 GHz | 0.5 Hz-<br>2.94912 GHz | ~ 120 fs typ | 72 QFN   |

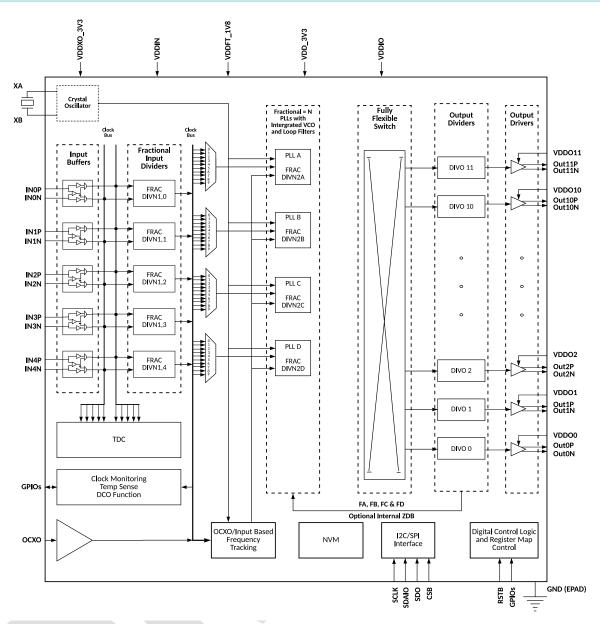

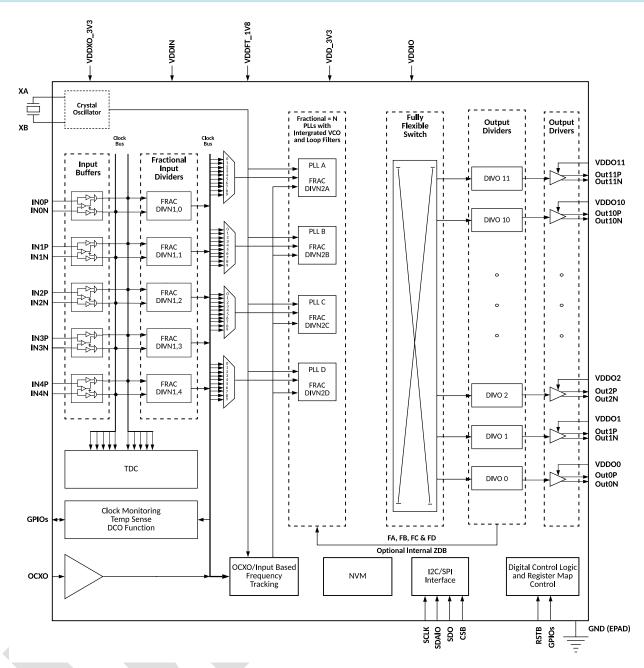

Figure 1 Functional Overview

# **Table of Contents**

| General Description          | 1  |

|------------------------------|----|

| Features                     | 1  |

| Table of Contents            |    |

| List of Tables               | 4  |

| List of Figures              |    |

| 1 Pin Description            |    |

| 2 Electrical Characteristics |    |

| 3 Functional Description     |    |

| 4 Package Information        |    |

| 5 Revision History           |    |

| 6 Trademarks                 | 27 |

| 7 Contact Information        | 29 |

# **List of Tables**

| Table 1 Pin Description                                   | 6  |

|-----------------------------------------------------------|----|

| Table 2 Absolute Maximum Ratings                          |    |

| Table 3 Operating Temperature and Thermal Characteristics | 10 |

| Table 4 Input Clock Characteristics                       | 12 |

| Table 5 Serial Data and Clock Input, GPIOs                | 13 |

| Table 6 Output Serial and Status Pin                      | 13 |

| Table 7 Output Clock Characteristics                      | 14 |

| Table 8 Fault Monitoring Indicators                       | 16 |

| Table 9 Crystal Requirements                              | 17 |

| Table 10 Output RMS Jitter in Frequency Translation Modes | 18 |

| Table 11 Close-In Offset Phase Noise                      | 18 |

| Table 12 Power Supply Rejection                           |    |

| Table 13 Adjacent Output Cross Talk                       |    |

| Table 14 Output Clock Specifications                      | 19 |

| Table 15 PIF Description                                  |    |

| Table 16 Revision History                                 | 27 |

# **List of Figures**

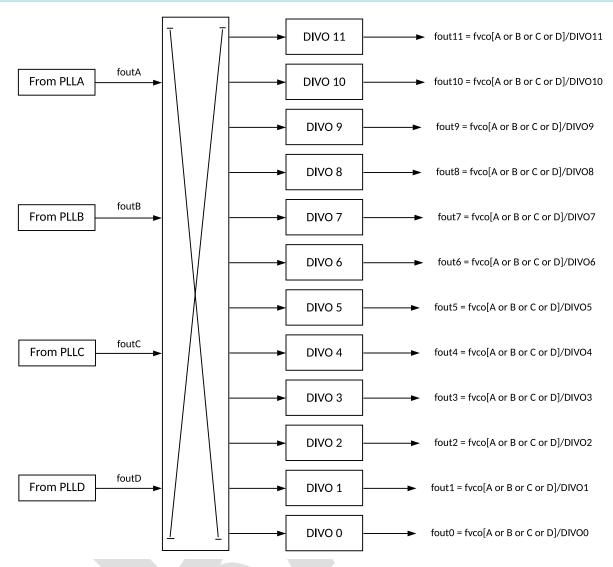

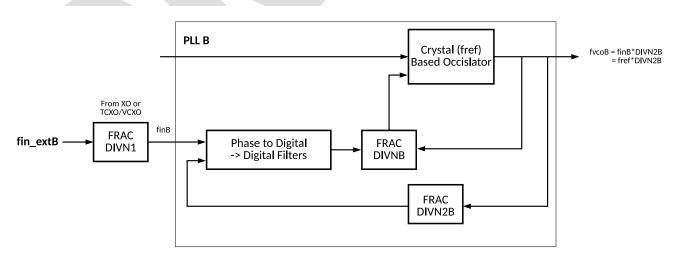

| Figure 1 Functional Overview             | 2  |

|------------------------------------------|----|

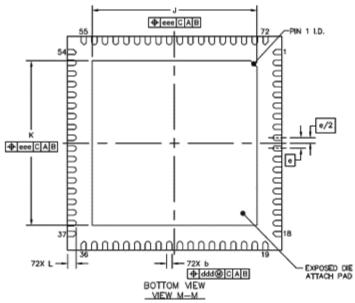

| Figure 2 Au5508 Pin Configuration        |    |

| Figure 3 Au5508 Functional Block Diagram |    |

| Figure 4 Output Clock Distribution       |    |

| Figure 5 PLL Internals                   | 24 |

| Figure 6 Package Information             |    |

# 1 Pin Description

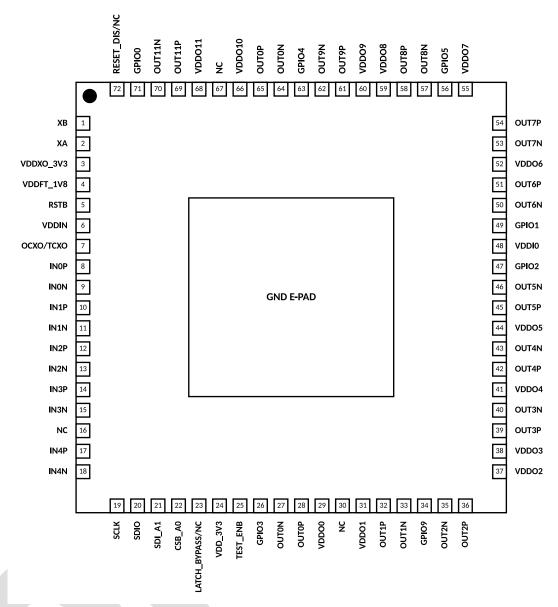

Figure 2 Au5508 Pin Configuration

**Table 1 Pin Description**

| Pin<br>No | Name      | I/O Type | Voltage Level          | Default<br>Pull Up/<br>Down | Description                                                                                                      |

|-----------|-----------|----------|------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------|

| 1         | ХВ        | Output   |                        |                             | Crystal Output. Crystal connects to this pin.<br>Leave unconnected if External oscillator is<br>connected to XA. |

| 2         | XA        | Input    | < 1.4 V                |                             | Crystal Input. External reference clock input.                                                                   |

| 3         | VDDXO_3V3 | Power    | 2.5 V – 3.6 V          |                             | Analog Power supply for Crystal Oscillator                                                                       |

| 4         | VDDFT_1V8 | Power    | 1.71 V – 2 V           |                             | Analog Power Supply for Frequency tracking PLL, Input TDC and Clock Monitors.                                    |

| 5         | RSTB      | Reset    | VDDIO (Pin 48)         | Pull up                     | Reset Input                                                                                                      |

| 6         | VDDIN     | Power    | 1.71 V/2.5 V/<br>3.6 V |                             | Analog Power Supply for Input buffers and dividers.                                                              |

| Pin<br>No | Name                 | I/O Type      | Voltage Level  | Default<br>Pull Up/<br>Down | Description                                                                                                                                                             |

|-----------|----------------------|---------------|----------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7         | осхо/тсхо            | Input         | -0.5V – 3.6 V  |                             | Clock reference input. A low wander input such as an OCXO or TCXO clock can be applied on this input. Alternatively it can be used as an extra single ended CMOS input. |

| 8         | IN0P                 | Input         | -0.5V – 3.6 V  |                             | Clock + for differential clock input. Single ended Input clock.                                                                                                         |

| 9         | INON                 | Input         | -0.5V – 3.6 V  |                             | Clock - for differential clock input. Single ended Input clock.                                                                                                         |

| 10        | IN1P                 | Input         | -0.5V – 3.6 V  |                             | Clock + for differential clock input. Single ended Input clock.                                                                                                         |

| 11        | IN1N                 | Input         | -0.5V – 3.6 V  |                             | Clock - for differential clock input. Single ended Input clock.                                                                                                         |

| 12        | IN2P                 | Input         | -0.5V – 3.6 V  |                             | Clock + for differential clock input. Single ended Input clock.                                                                                                         |

| 13        | IN2N                 | Input         | -0.5V – 3.6 V  |                             | Clock - for differential clock input. Single ended Input clock.                                                                                                         |

| 14        | IN3P                 | Input         | -0.5V – 3.6 V  |                             | Clock + for differential clock input. Single ended Input clock.                                                                                                         |

| 15        | IN3N                 | Input         | -0.5V – 3.6 V  |                             | Clock - for differential clock input. Single ended Input clock.                                                                                                         |

| 16        | NC                   | No<br>Connect |                |                             | Pin not bonded.                                                                                                                                                         |

| 17        | IN4P                 | Input         | -0.5V – 3.6 V  |                             | Clock + for differential clock input. Single ended Input clock.                                                                                                         |

| 18        | IN4N                 | Input         | -0.5V – 3.6 V  |                             | Clock - for differential clock input. Single ended Input clock.                                                                                                         |

| 19        | SCLK                 | I/O           | VDDIO (Pin 48) | Pull Up                     | Serial Clock for I2C/SPI Mode                                                                                                                                           |

| 20        | SDIO                 | I/O           | VDDIO (Pin 48) | Pull Up                     | I/O data port in I2C/3W SPI. Output port in 4W SPI mode.                                                                                                                |

| 21        | SDI_A1               | I/O           | VDDIO (Pin 48) | Pull Up                     | Input data port in 4W SPI. Optional I2C Address bit.                                                                                                                    |

| 22        | CSB_A0               | Input         | VDDIO (Pin 48) | Pull Up                     | Input port as chip select in SPI mode. Optional I2C Address bit.                                                                                                        |

| 23        | LATCH_BYPAS<br>S/ NC | Input         | VDDIO (Pin 48) | Pull Down                   | Enable bypass Wake GPIO latching/ No Connect for parts where GPIO latching function is needed. There is a default internal pull down resistor of 25k.                   |

| 24        | VDD_3V3              | Power         | 2.5 V – 3.6 V  |                             | Analog PLL Power Supply.                                                                                                                                                |

| 25        | TEST_ENB             | Input         | VDDIO (Pin 48) | Pull Up                     | Enable DFT Test Mode.                                                                                                                                                   |

| 26        | GPIO3                | I/O           | VDDIO (Pin 48) | Pull Down                   | Configurable as per NVM bits.                                                                                                                                           |

| 27        | OUT0N                | Output        | VDD00          |                             | Clock – for differential Output. Single ended CMOS Output.                                                                                                              |

| 28        | OUT0P                | Output        | VDDO0          |                             | Clock + for differential Output. Single ended CMOS Output.                                                                                                              |

| 29        | VDDO0                | Power         | 1.71 V – 3.6 V |                             | Power supply for OUT0 drivers.                                                                                                                                          |

| 30        | NC                   | No<br>Connect |                |                             | Pin not bonded.                                                                                                                                                         |

| 31        | VDDO1                | Power         | 1.71 V- 3.6 V  |                             | Power supply for OUT1 drivers.                                                                                                                                          |

| 32        | OUT1P                | Output        | VDDO1          |                             | Clock + for differential Output. Single ended CMOS Output.                                                                                                              |

| 33        | OUT1N                | Output        | VDDO1          |                             | Clock - for differential Output. Single ended CMOS Output.                                                                                                              |

| 34        | GPIO9                | I/O           | VDDIO (Pin 48) | Pull Up                     | Used I2C/SPI select during power up. Configurable as per NVM bits.                                                                                                      |

| Pin<br>No | Name   | I/O Type      | Voltage Level  | Default<br>Pull Up/<br>Down | Description                                                |

|-----------|--------|---------------|----------------|-----------------------------|------------------------------------------------------------|

| 35        | OUT2N  | Output        | VDDO2          |                             | Clock – for differential Output. Single ended CMOS Output. |

| 36        | OUT2P  | Output        | VDDO2          |                             | Clock + for differential Output. Single ended CMOS Output. |

| 37        | VDDO2  | Power         | 1.71 V- 3.6 V  |                             | Power supply for OUT2 drivers.                             |

| 38        | VDDO3  | Power         | 1.71 V – 3.6 V |                             | Power supply for OUT3 drivers.                             |

| 39        | OUT3P  | Output        | VDDO3          |                             | Clock + for differential Output. Single ended CMOS Output. |

| 40        | OUT3N  | Output        | VDDO3          |                             | Clock - for differential Output. Single ended CMOS Output. |

| 41        | VDDO4  | Power         | 1.71 V – 3.6V  |                             | Power supply for OUT4 drivers.                             |

| 42        | OUT4P  | Output        | VDDO4          |                             | Clock + for differential Output. Single ended CMOS Output. |

| 43        | OUT4N  | Output        | VDDO4          |                             | Clock - for differential Output. Single ended CMOS Output. |

| 44        | VDDO5  | Power         | 1.71 V- 3.6 V  |                             | Power supply for OUT5 drivers.                             |

| 45        | OUT5P  | Output        | VDDO5          |                             | Clock + for differential Output. Single ended CMOS Output. |

| 46        | OUT5N  | Output        | VDDO5          |                             | Clock - for differential Output. Single ended CMOS Output. |

| 47        | GPIO2  | I/O           | VDDIO (Pin 48) | Pull Up                     | Configurable as per NVM bits.                              |

| 48        | VDDIO  | Power         | 1.71 V- 3.6 V  |                             | GPIO/Serial Interface port Power Supply.                   |

| 49        | GPIO1  | I/O           | VDDIO (Pin 48) | Pull Up                     | Configurable as per NVM bits.                              |

| 50        | OUT6N  | Output        | VDDO6          |                             | Clock – for differential Output. Single ended CMOS Output. |

| 51        | OUT6P  | Output        | VDDO6          |                             | Clock + for differential Output. Single ended CMOS Output. |

| 52        | VDDO6  | Power         | 1.71 V- 3.6 V  |                             | Power supply for OUT6 drivers.                             |

| 53        | OUT7N  | Output        | VDDO7          |                             | Clock – for differential Output. Single ended CMOS Output. |

| 54        | OUT7P  | Output        | VDDO7          |                             | Clock + for differential Output. Single ended CMOS Output. |

| 55        | VDDO7  | Power         | 1.71 V- 3.6 V  |                             | Power supply for OUT7 drivers.                             |

| 56        | GPIO5  | I/O           | VDDIO (Pin 48) | Pull Up                     | Configurable as per NVM bits.                              |

| 57        | OUT8N  | Output        | VDDO8          |                             | Clock – for differential Output. Single ended CMOS Output. |

| 58        | OUT8P  | Output        | VDDO8          |                             | Clock + for differential Output. Single ended CMOS Output. |

| 59        | VDD08  | Power         | 1.71 V– 3.6 V  |                             | Power supply for OUT8 drivers.                             |

| 60        | VDDO9  | Power         | 1.71 V- 3.6 V  |                             | Power supply for OUT9 drivers.                             |

| 61        | OUT9P  | Output        | VDDO9          |                             | Clock + for differential Output. Single ended CMOS Output. |

| 62        | OUT9N  | Output        | VDDO9          |                             | Clock - for differential Output. Single ended CMOS Output. |

| 63        | GPIO4  | I/O           | VDDIO (Pin 48) | Pull Up                     | Configurable as per NVM bits.                              |

| 64        | OUT10N | Output        | VDDO10         |                             | Clock – for differential Output. Single ended CMOS Output. |

| 65        | OUT10P | Output        | VDDO10         |                             | Clock + for differential Output. Single ended CMOS Output. |

| 66        | VDDO10 | Power         | 1.71 V- 3.6 V  |                             | Power supply for OUT10 drivers.                            |

| 67        | NC     | No<br>Connect |                |                             | Pin not bonded.                                            |

| Pin<br>No | Name         | I/O Type | Voltage Level  | Default<br>Pull Up/<br>Down | Description                                                |

|-----------|--------------|----------|----------------|-----------------------------|------------------------------------------------------------|

| 68        | VDDO11       | Power    | 1.71 V- 3.6 V  |                             | Power supply for OUT11 drivers.                            |

| 69        | OUT11P       | Output   | VDDO11         |                             | Clock + for differential Output. Single ended CMOS Output. |

| 70        | OUT11N       | Output   | VDDO11         |                             | Clock - for differential Output. Single ended CMOS Output. |

| 71        | GPIO0        | I/O      | VDDIO (Pin 48) | Pull Down                   | Configurable as per NVM bits.                              |

| 72        | RESET_DIS/NC | I/O      | < 3.6 V        | Pull Down                   | Disables Hard reset when pulled high.                      |

| ePad      | Ground       |          | 0 V            |                             | Ground Pad                                                 |

### **2 Electrical Characteristics**

**Table 2 Absolute Maximum Ratings**

| Description                                                 | Conditions                                                                       | Symbol                                  | Min   | Тур | Max   | Units |

|-------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------|-------|-----|-------|-------|

| Supply Voltages                                             | Reference XO Supply<br>FTPLL Supply<br>Input Supply<br>PLL Supply<br>GPIO Supply | VDDXO_3V3 VDDFT_1V8 VDDIN VDD_3V3 VDDIO | -0.5  |     | +3.63 | V     |

| Output bank supply voltage                                  | Output Driver Supply                                                             | V <sub>DDO</sub>                        | -0.5  |     | +3.63 | V     |

| Input voltage, All Inputs                                   | Relative to GND Clock Inputs OCXO Input GPIO inputs                              | V <sub>IN</sub>                         | -0.5  |     | +3.63 | V     |

| XO Inputs                                                   | Relative to GND                                                                  | V <sub>XO</sub>                         | -0.5  |     | +1.4  | V     |

| I2C Bus input voltage                                       | SCLK<br>SDIO                                                                     | V <sub>INI2C</sub>                      | -0.5  |     | +3.63 | V     |

| SPI Bus input voltage                                       | SDI_A1<br>CSB_A0                                                                 | VINSPI                                  | -0.5  |     | +3.63 | V     |

| Storage temperature                                         | Non-functional, Non-<br>Condensing                                               | Ts                                      | -55   |     | +150  | °C    |

| Programming Temperature                                     |                                                                                  | T <sub>PROG</sub>                       | +25   |     | +85   | °C    |

| Maximum Junction Temperature in Operation                   |                                                                                  | T <sub>JCT</sub>                        |       |     | +125  | °C    |

| Programming Voltage (for Programming the OTP (Fuse Memory). |                                                                                  | VPROG                                   | 2.375 | 2.5 | 2.625 | V     |

| ESD (human body model)                                      | JESD22A-114                                                                      | ESDHBM                                  |       |     | 2000  | V     |

| ESD (charge device model)                                   |                                                                                  | ESD <sub>CDM</sub>                      |       |     | 500   | V     |

| Latch Up                                                    | JEDEC JESD78D                                                                    | LU                                      |       |     | 100   | mA    |

- Exceeding maximum ratings may shorten the useful life of the device.

- Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or at any other conditions beyond those indicated under the DC Electrical Characteristics is not implied.

- Exposure to Absolute-Maximum-Rated conditions for extended periods may affect device reliability or cause permanent device damage.

- Any pin category not covered here has a default minimum rating of -0.5 V and a default maximum rating of 3.63 V.

**Table 3 Operating Temperature and Thermal Characteristics**

| Description                             | Conditions     | Symbol | Min  | Тур  | Max  | Units |  |

|-----------------------------------------|----------------|--------|------|------|------|-------|--|

| Ambient temperature                     |                | TA     | -40  | -    | +85  | °C    |  |

| Junction temperature                    |                | TJ     |      |      | +125 | °C    |  |

| Au5508: 72-QFN package                  |                |        |      |      |      |       |  |

|                                         | Still Air      |        | 18.1 |      |      | °C/W  |  |

| Thermal Resistance Junction to Ambient  | Air Flow :1m/s | θја    | 15.3 |      |      |       |  |

|                                         | Air Flow: 2m/s |        | 14.3 |      |      |       |  |

| Thermal Resistance Junction to Case     |                | θυς    |      | 6.7  |      | °C/W  |  |

| Thermal Resistance<br>Junction to Board |                | Өлв    |      | 6.46 |      | °C/W  |  |

| Description                      | Conditions                                                                                                     | Symbol                            | Min         | Тур  | Max   | Units |

|----------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------|------|-------|-------|

| Au5508                           |                                                                                                                |                                   |             |      |       |       |

| PLL Supply                       | 3.3 V range: ± 10%                                                                                             | $V_{DD_3V3}$                      | 2.97        | 3.3  | 3.63  | V     |

| XO Supply                        | 3.3 V range: ±10%                                                                                              | V <sub>DDXO_3V3</sub>             | 2.97        | 3.3  | 3.63  | V     |

| FTPLL/TDC Supply                 | 1.8 V range: ±5%                                                                                               | V <sub>DDFT_1V8</sub>             | 1.71        | 1.8  | 1.89  | V     |

| Input Buffer Supply              | 3.3 V range: ±10%                                                                                              | V <sub>DDIN</sub>                 | 2.97        | 3.3  | 3.63  | V     |

|                                  | 1.8 V range: ±5%                                                                                               | V <sub>DDIO</sub>                 | 1.71        | 1.80 | 1.89  | V     |

| GPIO Supply                      | 2.5 V range: ±5%                                                                                               |                                   | 2.375       | 2.50 | 2.625 | V     |

|                                  | 3.3 V range: ±10%                                                                                              |                                   | 2.97        | 3.3  | 3.63  | V     |

|                                  | 1.8 V range: ±5%                                                                                               | $V_{DDO}$                         | 1.71        | 1.80 | 1.89  | V     |

| Output Driver Supply             | 2.5 V range: ±5%                                                                                               |                                   | 2.375       | 2.50 | 2.625 | V     |

|                                  | 3.3 V range: ±10%                                                                                              |                                   | 2.97        | 3.3  | 3.63  | V     |

| Power Dissipation (VDI           | D_3V3 = VDDXO_3V3=VD                                                                                           | DO = 3.3 V, V                     | /DDFT_1V8=1 | .8)  |       |       |

| Total Power Dissipation          | 4 PLLs, 12 Outputs<br>5 DE Inputs, OCXO PLL                                                                    | Pd                                |             | 2.2  |       | W     |

| (3.3V LVDS Outputs @<br>156.25M) | 1 PLL, 2 Outputs<br>1 DE                                                                                       |                                   |             | 500  |       | mW    |

| Supply Current                   |                                                                                                                |                                   |             |      |       |       |

| VDDIN                            | All Five DE Inputs assumed to be enabled                                                                       | I <sub>DDIN</sub>                 |             | 45   |       | mA    |

| VDD_3V3                          | All Four PLLs and All 12<br>Outputs enabled                                                                    | I <sub>DD_3V3</sub>               |             | 400  |       | mA    |

| VDDFT_1V8                        | FTPLL and All 10 Input<br>TDC enabled                                                                          | IDDFT_3V3                         |             | 30   |       | mA    |

| VDDXO_3V3                        | Crystal Oscillator                                                                                             | I <sub>DDXO_3V3</sub>             |             | 10   |       | mA    |

|                                  | LVPECL, output pair terminated 50 $\Omega$ to V <sub>TT</sub> (VDDO – 2 V).                                    | I <sub>DDO</sub> [1,2,3,5]        |             | 18   |       | mA    |

|                                  | LVPECL2, output pair terminated 50 $\Omega$ to V <sub>TT</sub> (VDDO - 2 V) or 0V without common mode current. |                                   |             | 19   |       | mA    |

| VDDO <sup>[4,7]</sup>            | CML, output pair terminated 50 $\Omega$ to VDDO                                                                | I <sub>DDO</sub> [1,5]            |             | 14   |       | mA    |

|                                  | HCSL, output pair with HCSL termination                                                                        | I <sub>DDO</sub> [1,5]            |             | 19   |       | mA    |

|                                  | LVDS output pair terminated with an AC or DC Coupled diff $100~\Omega$                                         | I <sub>DDO</sub> [1,5]            |             | 17   |       | mA    |

|                                  | LVCMOS, 250 MHz, 2.5V output, 5-pF load                                                                        | I <sub>DDO</sub> <sup>[5,6]</sup> |             | 22   |       | mA    |

<sup>1.</sup> LVPECL standard is supported for  $V_{DDO} = \{2.5 \text{ V}, 3.3 \text{ V}\}$ . LVPECL2, HCSL, CML and LVDS standards are supported for  $V_{DDO} = \{1.8 \text{ V}, 2.5 \text{ V}, 3.3 \text{ V}\}$ .

<sup>2.</sup> LVPECL mode provides 6 mA of common mode current on each output. LVPECL2 mode does not provide this common mode current.

<sup>3.</sup> A 50  $\Omega$  Termination resistor with a DC bias of  $V_{DDO} - 2 \text{ V}$  for LVPECL standards is supported for  $V_{DDO} = \{2.5 \text{ V}, 3.3 \text{ V}\}$ .

- 4. IDDOx Output driver supply current specified for one output driver in the table. This includes current in each of the output module that includes output dividers, drivers and clock distributions.

- 5. Refer to the Output Termination Information in Section 9 in the full Datasheet for the description of the various terminations that are supported.

- 6. Both P and N terminal are active in LVCMOS mode.

- 7. Current consumption doesn't account for load current. LVCMOS current include load current also.

#### **Table 4 Input Clock Characteristics**

| Parameter                                                                                                 | Conditions                                             | Symbol                | Min        | Тур            | Max             | Unit      |  |  |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------|------------|----------------|-----------------|-----------|--|--|

| Input Buffer with Differential DC or AC Coupled (See Input Slave Description for Termination information) |                                                        |                       |            |                |                 |           |  |  |

| Input Frequency Range                                                                                     | Differential                                           | - f <sub>IN</sub>     | 0.5        |                | 2100M           | Hz        |  |  |

| input i requeitey italige                                                                                 | All Single-ended signals (including LVCMOS)            | TIN                   | 0.5        | _              | 250M            | Hz        |  |  |

| PLL Input Frequency Range [1]                                                                             | PLL Input Frequency                                    | f <sub>IN_DPLL</sub>  | 0.5        | -              | 30M             | Hz        |  |  |

| Input Common Mode Voltage Range (for DC Coupled Differential Inputs)                                      | Differential DC coupled inputs; Defined as cross point | V <sub>CMR</sub>      | 0.25       |                | VDDIN –<br>0.85 | V         |  |  |

|                                                                                                           | f <sub>IN</sub> < 400 MHz                              |                       | 100        | _              | -               | mV        |  |  |

| Single Ended Peak to Peak Voltage [2]                                                                     | 400 MHz < f <sub>IN</sub> < 750 MHz                    | VD                    | 225        | _              | -               | mV        |  |  |

| Vollage                                                                                                   | 750 MHz < f <sub>IN</sub> < 2100 MHz                   | VP <sub>IN</sub>      | 350        | _              | -               | mV        |  |  |

|                                                                                                           |                                                        |                       |            |                |                 |           |  |  |

| Single Ended AC Coupled                                                                                   | input- — DC-coupled (IN0P/N,                           | IN1P/N, IN2P/N,       | N3P/N, IN4 | IP/N, OCXO Inp | ut)             |           |  |  |

| Single Ended AC Coupled Inputs (Single Ended Peak to Peak Input) [3]                                      | AC-Coupled f <sub>IN</sub> < 250 MHz                   | f <sub>IN,SE_AC</sub> | 500        | -              | 3600            | mV        |  |  |

| Slew Rate [4]                                                                                             |                                                        | SR                    | 400        | _              |                 | V/µs      |  |  |

| Duty Cycle                                                                                                |                                                        | DC                    | 40         | _              | 60              | %         |  |  |

| Input Capacitance                                                                                         |                                                        | C <sub>IN</sub>       | _          | 0.3            | _               | pF        |  |  |

| Input Resistance                                                                                          | AC Coupled SE                                          | R <sub>IN</sub>       | -          | 15             | _               | kΩ        |  |  |

| Pulsed CMOS Input Buffe                                                                                   | r — DC-coupled (IN0P/N, IN1P                           | /N, IN2P/N, IN3P/I    | N, IN4P/N, | OCXO Input)    |                 |           |  |  |

| Input Frequency                                                                                           |                                                        | fin_pulsed_cmos       | 0.5        | _              | 250M            | Hz        |  |  |

| Leaved Mallana                                                                                            |                                                        | VIL                   | -0.2       | _              | 0.4             | V         |  |  |

| Input Voltage                                                                                             |                                                        | V <sub>IH</sub>       | 0.8        | _              | VDDIN           | V         |  |  |

| Slew Rate [4]                                                                                             |                                                        | SR                    | 400        | _              | _               | V/µs      |  |  |

| Duty Cycle                                                                                                |                                                        | DC                    | 40         | _              | 60              | %         |  |  |

| Input Resistance                                                                                          |                                                        | R <sub>IN</sub>       | _          | 30             | _               | kΩ        |  |  |

| Reference Clock (Applied                                                                                  | to XA), Can be external XO                             |                       |            | •              |                 |           |  |  |

| Reference Clock                                                                                           | Range for best jitter                                  | _                     | 48         | -              | 160             | MHz       |  |  |

| Frequency                                                                                                 | Overall supported range                                | F <sub>IN_REF</sub>   | 25         | -              | 160             | MHz       |  |  |

| least Vallage 2                                                                                           | Single Ended peak to peak                              | $V_{IN\_SE}$          | 365        | -              | 2000            | mVpp_se   |  |  |

| Input Voltage Swing                                                                                       | Differential peak to peak                              | V <sub>IN_DIFF</sub>  | 365        | -              | 2500            | mVpp_diff |  |  |

| Slew rate                                                                                                 |                                                        | SR                    | 400        | -              | -               | V/us      |  |  |

| Duty Cycle                                                                                                |                                                        | DC                    | 40         | -              | 60              | %         |  |  |

- 1. For proper device operation, the input frequency is internally divided down to 30 MHz or less (PLL Phase Detector maximum frequency = 30 MHz). This is achieved using internal dividers in the chip.

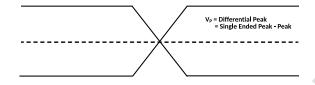

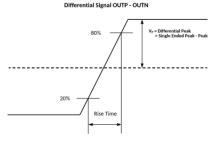

- 2. VP<sub>IN</sub> is the single-ended peak-peak of the input signal which is equal to the differential peak. This is the swing requirement for both AC and DC coupled differential inputs where the swing is considered at the pin inputs.

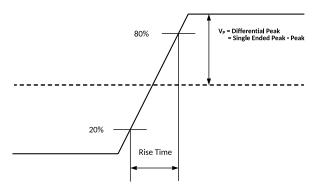

#### Differential Signal OUTP - OUTN

Single Ended Signals (OUTP, OUTN)

- 3. AC Coupled input assumed with series capacitance for single ended AC Coupled inputs. Swing requirement at device pins for

- 4. Minimum slew rate specification is for best noise performance.

Table 5 Serial Data and Clock Input, GPIOs

| Parameter              | Condition  | Symbol           | Min                       | Тур | Max                       | Unit |

|------------------------|------------|------------------|---------------------------|-----|---------------------------|------|

| Innut Valtage          |            | VIL              | 1                         | _   | $0.3 \times V_{DDIO}^{1}$ | V    |

| Input Voltage          |            | VIH              | $0.7 \times V_{DDIO}^{1}$ | _   | VDDIO                     | V    |

| Input Capacitance      |            | C <sub>IN</sub>  |                           | 1   | _                         | pF   |

| Input Resistance       |            | R <sub>IN</sub>  | _                         | 25  | _                         | kΩ   |

| Minimum Pulse Width    | FINC, FDEC | PW               | 100                       | _   | _                         | ns   |

| Minimum RESET duration |            | T <sub>RES</sub> | 100                       |     |                           | μs   |

| Update Rate            | FINC, FDEC | Fur              | _                         | _   | 1                         | μs   |

#### Notes:

- 1. VDDIO is the voltage used for all the status GPIOs and the serial interface. This is the voltage applied on Pin 48

- 2. FINC/FDEC are the increment and decrement for the DCO opertaion from the pins

### **Table 6 Output Serial and Status Pin**

| Parameter             | Test Condition           | Symbol          | Min                      | Тур | Max                      | Unit |  |  |

|-----------------------|--------------------------|-----------------|--------------------------|-----|--------------------------|------|--|--|

| All VDDIO based GPIOs |                          |                 |                          |     |                          |      |  |  |

| Output Voltage -      | $I_{OH} = -2 \text{ mA}$ | V <sub>OH</sub> | V <sub>DDIO</sub> x 0.75 | _   | _                        | V    |  |  |

|                       | $I_{OL} = 2 \text{ mA}$  | Vol             | _                        | _   | V <sub>DDIO</sub> x 0.25 | V    |  |  |

#### Notes:

1. VDDIO is the voltage used for all the status GPIOs and the serial interface. This is the voltage applied on Pin 48

# **Table 7 Output Clock Characteristics**

| Description                                                                                                       | Conditions                                                                                                                                                                                                                          | Symbol                                 | Min                                   | Тур    | Max   | Units  |

|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------------|--------|-------|--------|

| Differential output                                                                                               |                                                                                                                                                                                                                                     | Syllibol                               | IVIIII                                | Тур    | IVIAA | Office |

| frequency continuous support [1],[2]                                                                              | Differential output standards                                                                                                                                                                                                       |                                        | 0.5                                   |        | 800M  | Hz     |

| Differential output<br>frequency Selective<br>Higher Frequency<br>Support (For >800MHz<br>outputs) <sup>[3]</sup> | Differential Output<br>Standards                                                                                                                                                                                                    | F <sub>OUT,DIFF</sub> <sup>[1,3]</sup> | 61.44M* {15<br>921.6M, 122<br>1966.08 | Hz     |       |        |

| Single ended output frequency                                                                                     | LVCMOS outputs                                                                                                                                                                                                                      | F <sub>OUT,SE</sub>                    | 1                                     |        | 250 M | Hz     |

| PLL loop bandwidth                                                                                                | Programmable                                                                                                                                                                                                                        | F <sub>BW</sub>                        | 0.00009                               |        | 4000  | Hz     |

| Jitter peaking <sup>[4]</sup>                                                                                     | Meets SONET Jitter<br>Peaking requirements<br>in closed loop (see<br>footnote)                                                                                                                                                      | J <sub>PEAK</sub>                      |                                       |        | 0.1   | dB     |

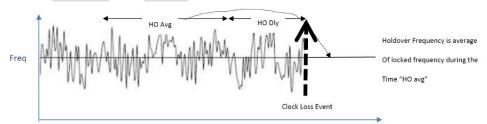

| Time delay before the<br>Historical average for<br>output frequency is<br>considered.                             | Programmable in register map                                                                                                                                                                                                        | H <sub>DELAY</sub> <sup>[5]</sup>      | 0.035                                 | 0.5    | 35    | S      |

| Length of time for<br>which the Average of<br>the frequency is<br>considered                                      | Programmable in register map                                                                                                                                                                                                        | H <sub>AVG</sub> <sup>[5]</sup>        | 0.07                                  | 1      | 70    | S      |

| Power Supply to I2C or<br>SPI interface ready                                                                     | No I2C or SPI<br>transaction valid till<br>10ms after all power<br>supplies are ramped to<br>90% of final value.                                                                                                                    | T <sub>START</sub>                     |                                       |        | 10    | ms     |

| Hold Time for GPIO<br>Latching <sup>[6]</sup>                                                                     | Hold time for GPIO<br>latched inputs available<br>on the GPIOs after the<br>RSTB pin is driven from<br>low to high                                                                                                                  | T <sub>HOLD</sub> <sup>[6]</sup>       | 1                                     |        |       | ms     |

| DCO Mode Frequency<br>Step Resolution <sup>[7]</sup>                                                              | Frequency Increment or Decrement resolution. This is controlled through the register map.                                                                                                                                           | F <sub>RES,DCO</sub> <sup>[7]</sup>    |                                       | 0.0625 |       | Ppt    |

| Output Phase Shift <sup>[8]</sup>                                                                                 | Resolution for output delay between clocks from same PLL. Resolution Programmable per output clock with this resolution for a total delay range of ±T/2 where T is the time period of the output clock                              | T <sub>RESO</sub> [8]                  |                                       | 35     |       | Ps     |

| Output Skew <sup>[9]</sup>                                                                                        | Skew between outputs from the same PLL set up with same phase shift code                                                                                                                                                            | T <sub>SKEW</sub> <sup>[9]</sup>       | -50                                   |        | 50    | Ps     |

| Input Phase Shift<br>Resolution <sup>[10]</sup>                                                                   | Programmable delay resolution for all outputs that are locked to a particular input. Input phase shift is programmable per input clock with this resolution for a total delay of ±T/2 where T is the time period of the input clock | T <sub>RESI</sub> <sup>[10]</sup>      | 10                                    |        |       | Ps     |

| PLL Lock Time <sup>[11]</sup>                                                                                     | Standard Mode                                                                                                                                                                                                                       | T <sub>LOCK</sub>                      |                                       | 300m   |       | Sec    |

| Description                                                                                        | Conditions                                                                                                          | Symbol                           | Min  | Тур | Max | Units |

|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------|------|-----|-----|-------|

|                                                                                                    | 1 PPS Mode,<br>Frequency Lock to<br>within 1ppb                                                                     | T <sub>LOCK_FREQ_1</sub>         |      |     | 30  | Sec   |

|                                                                                                    | 1 PPS Mode, Input to<br>Output Phase Error <<br>+/- 30ns                                                            | TLOCK_PHASE_                     |      |     | 30  | Sec   |

| Maximum Phase Hit <sup>[12]</sup>                                                                  | Default PBO Hitless<br>Switching Mode (no<br>phase propagation)                                                     | T <sub>MAX</sub> <sup>[12]</sup> | -25  |     | 25  | Ps    |

| Input to Output Delay in external ZDB mode (external ZDB with feedback on the PCB) <sup>[13]</sup> | Any output to any input external feedback is possible. Supported for all PLLs. Multiple PLLs                        | T <sub>ZDELAY</sub>              | -100 |     | 100 | Ps    |

| Temperature Variation of delay in external ZDB mode <sup>[13]</sup>                                | in external ZDB are supported concurrently                                                                          | T <sub>ZDELAY,TMP</sub>          |      |     | 1   | ps/C  |

| Internal ZDB Mode<br>Input to Output Delay <sup>[14]</sup>                                         | Supported for all PLLs. Multiple PLLs in internal ZDB are supported concurrently.                                   | $T_{ZDELAY,INT}$                 | -500 |     | 500 | Ps    |

| Uncertainty in Input to<br>Output Delay                                                            | Maximum variation in<br>the static delay from<br>input to output clock<br>between repeated<br>power ups of the chip | $\Delta T_{DELAY}$               | -175 |     | 175 | Ps    |

| PLL Pull Range                                                                                     |                                                                                                                     | ωР                               |      | 500 |     | Ppm   |

- 1. The continuous frequency support implies that all output frequencies till 800 MHz are available with no gaps.

- 2. The VCOs support two ranges: A Low Band Range of 4843.75 MHz to 5898.24 MHz and a High Band Range of 6875 MHz to 8000 MHz. Along with the fully flexibly output multiplexer for the output clocks, this provides for customer use cases to be easily supported with several concurrent frequencies for application scenarios possible from a single PLL.

- 3. Specific multiples of 61.44 MHz are provided for Wireless applications. Please contact Aura Semiconductor for more frequency options and details.

- 4. Jitter peaking limit of < 0.1 dB can be enabled as an option for cases (such as SONET) where there is such a critical requirement. For other cases, the jitter peaking can be made slightly higher to enable faster transients and lock characteristics.

- 5. Hitless Switching enables PLL to switch between input clocks when the current clock is lost,

- a. Clock Loss can be defined as a specified number of consecutive missing pulses.

- b. Priority list for the input clocks can be set in the register map independently for each PLL.

- c. Output is truly hitless (no phase transient and 0 ppb relative error in frequency) for exactly same frequency input clocks that are switched in Phase Build Out Mode. Please refer to the relevant clock switching application notes for various switching modes/options available in Au5508.

- d. Hitless switching support is both revertive and non-revertive

- e. Revertive / Non-revertive Support: Assume Clock Input 0 is lost and switch is made to Clock Input 1. Then, PLL reverts to Clock Input 0 when it becomes valid again in Revertive mode. It does not switch back to Clock Input 0 even when it becomes valid again in the non-Revertive mode.

- f. Entering hold over mode is supported with the frequency frozen at a historical average determined from the H<sub>DELAY</sub> and H<sub>AVG</sub> settings.

- 6. The Au5508 chip provides a GPIO latching function that allows for certain GPIOs to function as latched GPIOs that are latched along with the release of chip reset (using the RSTB pin) and can the same pin is released for other functions in steady state.

- a. This requires the RSTB pin to be held low and released from low to high ONLY when all supplies to the chip have crossed 90% of their final value.

- b. This further requires that the GPIOs whose inputs are used for GPIO latching should "Hold" the expected value for latching for at least 1ms of time after the RSTB pin has reached 90% of the VDDIO supply.

- 7. The 1/16 ppt specification is for the smallest frequency step resolution available. Larger frequency step resolutions up to 100 ppm can be used also. The frequency resolution for the DCO mode frequency step is independently programmable for each DCO step.

- a. DCO steps are applicable on both XO referenced PLLs (free run) and input referenced PLL (sync mode)

- b. DCO step size is programmed in the programmable interface (PIF) using the serial I2C or SPI interface

- c. DCO is enacted in response to a trigger. This trigger can be provided either with a register based write through the serial interface or a pin-based trigger where a GPIO is programmed for the purpose of the increment and decrement DCO trigger.

- 8. The delay referred to here is delay between outputs from the same PLL. Such a delay can delay a clock by as much as 180 degrees which is half of a time period of the output clock with the resolution of 35 ps.

- a. All output clocks from one specific PLL are phase aligned by default. Relative delay adjustment is then possible on each clock individually as defined by the T<sub>RES</sub> parameter for a total delay range of ±T/2 where T is the time period of the output clock.

- 9. This is the skew between outputs from the same PLL such that they are set up with the same relative output phase shift code.

- 10. The delay referred to here is from input to output hence it appears in the system as an input phase shift. All outputs from a PLL that is locked to a particular input can move by as much as 180 degrees of the input clock for the PLL (which is half the time period for the PLL input clock) and with a resolution of +/- 10ps.

- 11. For low PLL Loop Bandwidths, wake up time can be very large unless the speed up features are used. The speed up feature provides the user options to use a completely independent time constants for the wake-up transitioning to the regular bandwidth after frequency and phase are locked

- a. Fast Lock Bandwidth needs to be less than 100 times smaller than the input clock frequency (divided input at PLL phase detector) for stable and bounded (in time) lock trajectory of the PLL

- b. 1 PPS locking has extra features inbuilt especially with respect to facilitating the sub +/- 30ns phase lock in addition to the frequency lock within the 30 seconds specification

- 12. This test is for 2 inputs at 8M that are switched to get a 156.25M output.

- 13. Both input and feedback at 8MHz with the delays exactly matched and same slew for both for the chip

- 14. Internal ZDB mode is supported concurrently on any number of PLLs. The delay specification here is for delay between the input port and output port of the chip.

- 15. With PLL A and B configured in Internal ZDB mode, only internal feedback frequency can be brought out on OUT0 and with PLL C and D configured in Internal ZDB mode, only internal feedback frequency can be brought out on OUT11.

#### **Table 8 Fault Monitoring Indicators**

| Description                                                          | Conditions                                                                                                                                                                     | Symbol                 | Min  | Тур | Max   | Units  |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-----|-------|--------|

| Clock Loss Indicator<br>Thresholds                                   | Clock Loss Indicators can be set on any of the four inputs. Loss of 2 / 4 / 8 / 16 consecutive pulses can be used to indicate a clock loss.  Programmable in the register map. | CL <sub>x</sub> [1,4]  | 2    | 4   | 16    | Pulses |

| Fine Frequency Drift<br>Indicator<br>Thresholds: Step Size           | Frequency drift threshold is programmable in the                                                                                                                               |                        |      | ±2  |       | Ppm    |

| Fine Frequency Drift<br>Indicator<br>Thresholds: Hysteresis<br>Range | range with the step size resolution specified. Frequency drift hysteresis is                                                                                                   | FDx <sup>[2,3,4]</sup> | ±2   |     | ±500  | Ppm    |

| Fine Frequency Drift<br>Indicator<br>Thresholds: Range               | programmable in the range with the step size resolution specified.                                                                                                             |                        | ±2   |     | ±500  | Ppm    |

| Coarse Frequency Drift<br>Indicator Thresholds                       | Coarse Drift Indicators programmable from {Up to ±1600 ppm in steps of ± 100 ppm}                                                                                              |                        | ±100 |     | ±1600 | Ppm    |

| Phase Lock Loss<br>Indicator                                         | Provides phase locking indication for lock of the input and feedback clock phases with respect to each other for each PLL. This is particularly useful for 1 PPS lock          | LLPH                   | 1n   |     | 100u  | Sec    |

| Description                      | Conditions                                                                                                                                                                                                        | Symbol | Min  | Тур | Max   | Units |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|-----|-------|-------|

| Lock Loss Indicator<br>Threshold | Lock Loss Indicator threshold is programmable in the range specified from the following choices for setting and clearing LL: {±0.2, ±0.4} ppm, {±2, ±4} ppm, {±20, ±40} ppm, {±200, ±400} ppm, {±2000, ±4000} ppm | LL     | ±0.2 |     | ±4000 | Ppm   |

- 1. Clock Loss Indicators are used for:

- a. Hitless Switching Triggers

- b. Update in Status Registers in the register map

- 2. Frequency Drift Indicators can use any one of the ten input clocks or the Crystal / Reference input clock as the golden reference with respect to which FDx for all other clocks can be recorded in the Status Registers. FDx thresholds for each clock input for each clock can be set independently.

- 3. Coarse and Fine Frequency Drift indicators can be concurrently enabled. This enables the user to detect fast drifting frequencies since detecting fine drifts will take longer measurements.

- 4. Clock loss and Lock loss indicators are available as alerts on GPIO pins as described in Section 7.1 in the full Datasheet

- 5. Clock Loss can be combined with either of the frequency drift monitors (coarse and fine) to trigger the hitless switching event in the PLLs. The trigger for a hitless switching event in the PLL can therefore be either the Clock Loss event or either of Clock Loss or Frequency Drift.

#### **Table 9 Crystal Requirements**

| Description                | Conditions                                                                                                                  | Symbol                  | Min | Тур | Max | Units |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------|-----|-----|-----|-------|

| High Fundamental Freq      | uency Crystal Reference                                                                                                     | (HFF)                   |     |     | •   |       |

| Crystal Frequency          | Can be supported with a fundamental crystal of 100-160 MHz range.                                                           | XTALIN                  | 100 |     | 160 | MHz   |

| C0 cap for crystal         | Small range around CL                                                                                                       | XTAL <sub>C0</sub>      |     |     | 2   | pF    |

| CL cap for crystal         | only                                                                                                                        | XTALCL                  |     | 5   |     | pF    |

| ESR for crystal            | ESR defined at frequency of oscillation                                                                                     | XTALESR                 |     |     | 40  | Ω     |

| Rm1 for crystal            |                                                                                                                             | XTAL <sub>Rm1</sub>     |     |     | 20  | Ω     |

| Power delivered to crystal | Drive Level to the crystal                                                                                                  | XTAL <sub>PWR</sub>     |     | 100 |     | μW    |

| Low Frequency Fundan       | nental Crystal (LFF)                                                                                                        |                         |     |     |     |       |

| Crystal Frequency          | Can be supported with<br>a fundamental crystal<br>> 25 MHz range. For<br>Best Performance use<br>an LFF crystal<br>> 48 MHz | XTAL <sub>IN</sub>      | 25  |     | 54  | MHz   |

| C0 cap for crystal         | Small range around CL                                                                                                       | XTAL <sub>C0</sub>      |     |     | 2   | pF    |

| CL cap for crystal [2]     | only                                                                                                                        | XTALCL                  |     | 8   |     | pF    |

| ESR for crystal            | ESR defined at frequency of oscillation                                                                                     | XTAL <sub>ESR</sub> [1] |     |     | 40  | Ω     |

| Rm1 for crystal            |                                                                                                                             | XTAL <sub>Rm1</sub>     |     |     | 40  | Ω     |

| Power delivered to crystal | Drive Level to the crystal                                                                                                  | XTAL <sub>PWR</sub>     |     | 100 |     | μW    |

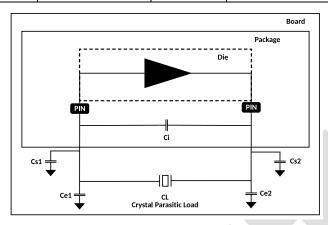

- 1. ESR relates to the motional resistance Rm with the relationship ESR = Rm (1 + CO/CL)2

- 2. The table specifies the Ci, Ce and Cs for the 54MHz XTAL with different CL. Ci is the internal differential capacitance offered by the chip whereas Ce (Ce=Ce1=Ce2) and Cs(Cs=Cs1=Cs2) are the Single Ended external and the stray cap on the PCB.

| XTAL              | Ci  | Се | Cs | Unit |

|-------------------|-----|----|----|------|

| 54MHz (CL = 8pF)  | 7.5 | 0  | 1  | pF   |

| 54MHz (CL = 12pF) | 8.1 | 7  | 1  | pF   |

**Table 10 Output RMS Jitter in Frequency Translation Modes**

| Description                                                            | Conditions                                                                        | Symbol                   | Min | Тур | Max | Units  |

|------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------|-----|-----|-----|--------|

| RMS Jitter for<br>12 kHz – 20 MHz<br>Integration Bandwidth             | Fout = 156.25 MHz<br>54 MHz Crystal [3]                                           |                          |     | 120 |     | fs rms |

| F <sub>IN</sub> = 38.88 MHz,<br>PLL BW = 100 Hz,<br>Single PLL Profile | IN = 38.88 MHz,<br>LL BW = 100 Hz,<br>FOUT = 156.25 MHz<br>54 MHz External XO [4] | RMS <sub>JIT</sub> [1,2] |     | 130 |     | fs rms |

- 1. For best noise performance in jitter attenuation mode, use lowest usable loop bandwidth for the PLL.

- 2. Does not include noise from the input clocks to the PLL

- 3. Crystal is assumed to meet the specifications mentioned in this data sheet

- 4. External XO with a CMOS drive such as TXC 7X54000007 is assumed

**Table 11 Close-In Offset Phase Noise**

| Description                                                                                                       | Conditions                 | Symbol            | Min | Тур  | Max | Units  |

|-------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------|-----|------|-----|--------|

|                                                                                                                   | Offset Frequency = 100 Hz  |                   |     | -103 |     |        |

| Phase Noise Skirt                                                                                                 | Offset Frequency = 1 kHz   |                   |     | -123 |     |        |

| F <sub>IN</sub> = 38.88 MHz<br>F <sub>OUT</sub> = 122.88 MHz,<br>PLL BW = 100 Hz<br>54 MHz Crystal <sup>[2]</sup> | Offset Frequency = 10 kHz  | PN <sup>[1]</sup> |     | -138 |     | dBc/Hz |

|                                                                                                                   | Offset Frequency = 100 kHz | FIN. 7            |     | -143 |     | UBC/HZ |

|                                                                                                                   | Offset Frequency = 1 MHz   |                   |     | -154 |     |        |

|                                                                                                                   | Offset Frequency = 10 MHz  |                   |     | -160 |     |        |

|                                                                                                                   | Offset Frequency = 100 Hz  |                   |     | -114 |     | dBc/Hz |

| Phase Noise Skirt                                                                                                 | Offset Frequency = 1 kHz   |                   |     | -128 |     |        |

| F <sub>IN</sub> = 38.88 MHz<br>F <sub>OUT</sub> = 122.88 MHz,                                                     | Offset Frequency = 10 kHz  | PN <sup>[1]</sup> |     | -138 |     |        |

| PLL BW = 100 Hz                                                                                                   | Offset Frequency = 100 kHz | FIN. 7            |     | -142 |     |        |

| 54 MHz External XO <sup>[3]</sup>                                                                                 | Offset Frequency = 1 MHz   |                   |     | -152 |     |        |

|                                                                                                                   | Offset Frequency = 10 MHz  |                   |     | -160 |     |        |

- 1. This is the noise contribution of the chip only without including the input and reference self-contributions.

- 2. Crystal is assumed to meet the specifications mentioned in this data sheet

- 3. External XO with a CMOS drive such as TXC 7X54000007 is assumed.

#### **Table 12 Power Supply Rejection**

| Description                                                                                              | Conditions      | Symbol                | Min | Тур | Max | Units |

|----------------------------------------------------------------------------------------------------------|-----------------|-----------------------|-----|-----|-----|-------|

| FOUT = 156.25 MHz,<br>FSPUR = 100 kHz,<br>BW = 100 Hz<br>PSRR on PLL Supply                              | VDD_3V3 = 3.3 V | PSRR <sub>VDD</sub>   |     | -80 |     | dBc   |

| $F_{OUT} = 156.25 \text{ MHz},$<br>$F_{SPUR} = 100 \text{ kHz},$<br>BW = 100  Hz<br>PSRR on Input Supply | VDDIN = 3.3 V   | PSRR <sub>VDDIN</sub> |     | -80 |     | dBc   |

| FOUT = 156.25 MHz,<br>FSPUR = 100 kHz,<br>BW = 100 Hz<br>PSRR on Output Driver<br>Supply                 | VDDO = 3.3 V    | PSRR <sub>VDDO</sub>  |     | -80 |     | dBc   |

#### Notes:

- 1. The PSRR is measured with a 50 mVpp sinusoid in series with the supply and checking the spurious level relative to the carrier on the output in terms of phase disturbance impact.

- 2. Output PSRR measured with LVDS standard which is the recommended standard for AC Coupled terminations

#### **Table 13 Adjacent Output Cross Talk**

| Description                               | Conditions  | Symbol            | Min | Тур | Max | Units |

|-------------------------------------------|-------------|-------------------|-----|-----|-----|-------|

| 156.25 M and 155.52 M on adjacent outputs | LVDS Output | X <sub>TALK</sub> |     | -75 |     | dBc   |

#### Notes:

- 1. Measured across adjacent outputs- All adjacent outputs are covered and the typical value for the worst-case output to output coupling is reported.

- 2. The adjacent output pairs are chosen at 155.52 MHz and 156.25 MHz frequencies.

- 3. This cross talk between outputs is mainly package dependent therefore terminated outputs are used for reporting these numbers ensuring that there is signal current in the bond wires.

#### **Table 14 Output Clock Specifications**

| Descriptions                                                                                                           | Conditions                                                      | Symbol                                        | Min       | Тур | Max   | Units |  |

|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------|-----------|-----|-------|-------|--|

| DC Electrical Specifications - LVCMOS output (Complementary Out of Phase Outputs or One CMOS Output per Output Driver) |                                                                 |                                               |           |     |       |       |  |

| Output High Voltage                                                                                                    | 4 mA load, VDD = 3.3 V                                          | V <sub>OH</sub>                               | VDDO-0.3  |     | -     | V     |  |

| Output High Voltage                                                                                                    | 4 mA load,<br>VDD = 1.8V and 2.5 V                              | V <sub>OH</sub>                               | VDDO-0.4  |     | -     | V     |  |

| Output Low Voltage                                                                                                     | 4 mA load                                                       | V <sub>OL</sub>                               |           |     | 0.3   | V     |  |

| DC Electrical Specification                                                                                            | DC Electrical Specifications - LVCMOS output (In Phase Outputs) |                                               |           |     |       |       |  |

| Output High Voltage                                                                                                    | 4 mA load, VDD = 3.3 V                                          | V <sub>OH</sub>                               | VDDO-0.35 |     | -     | V     |  |

| Output High Voltage                                                                                                    | Voltage 4 mA load, VDD = 2.5 V V <sub>OH</sub> VDDO-0.45        |                                               |           | -   | V     |       |  |

| Output High Voltage                                                                                                    | 4 mA load, VDD = 1.8 V                                          | mA load, VDD = 1.8 V V <sub>OH</sub> VDDO-0.5 |           |     | -     | V     |  |